# Evaluation of P-stop Structures in the N-side of N-on-N Silicon Strip Detector

Y. Unno<sup>a</sup>, H. Kitabayashi<sup>b</sup>, B. Dick<sup>g</sup>, T. Dubbs<sup>j</sup>, A. Grillo<sup>j</sup>, M. Ikeda<sup>b</sup>, Y. Iwata<sup>b</sup>, S. Kashigin<sup>j</sup>, E. Kitayama<sup>h</sup>, W. Kroeger<sup>j</sup>, T. Kohriki<sup>a</sup>, T. Kondo<sup>a</sup>, G. Moorhead<sup>g</sup>, D. Morgan<sup>k</sup>, I. Nakano<sup>h</sup>, T. Ohmoto<sup>b</sup>, T. Ohsugi<sup>b</sup>, P.W. Phillips<sup>i</sup>, J. Richardson<sup>1,f<sup>1</sup></sup>, W. Rowe<sup>j</sup>, H.F.-W. Sadrozinski<sup>j</sup>, K. Sato<sup>b</sup>, J. Siegrist<sup>e</sup>, E. Spencer<sup>j</sup>, H. Spieler<sup>e</sup>, R. Takashima<sup>d</sup>, G. Taylor<sup>g</sup>, S. Terada<sup>a</sup>, T. Umeda<sup>h</sup>, M. Wilder<sup>j</sup>, K. Wyllie<sup>c</sup>, and H. Yagi<sup>h</sup>

<sup>a</sup>Institute of Particle and Nuclear Studies, High Energy Accelerator Organization (KEK), Oho 1-1, Tsukuba, Ibaraki 305, Japan

<sup>b</sup>Department of Physics, Hiroshima University, Kagamiyama 1-3-1, Higashi-Hiroshima, Hiroshima 739, Japan

<sup>c</sup>Cavendish Laboratory, University of Cambridge, Madingley Road, Cambridge CB3 0HE, United Kingdom

<sup>d</sup>Department of Education, Kyoto University of Education, Fukakusa, Fushimi-ku, Kyoto 612, Japan

<sup>e</sup>Physics division, Lawrence Berkeley National Laboratory (LBNL), 1 Cyclotron Road, Berkeley, California 94720, U. S. A.

<sup>f</sup>Department of Physics, University of Liverpool, P. O. Box 147, Liverpool L69 7ZE, United Kingdom

<sup>g</sup>School of Physics, University of Melbourne, Parkville, Victoria 3052, Australia

<sup>h</sup>Department of Physics, Okayama University, Tsusima-naka 3-1-1, Okayama 700, Japan

<sup>i</sup>Particle Physics Department, Rutherford Appleton Laboratory (RAL), Chilton, Didcot, Oxon OX11 0QX, United Kingdom

<sup>j</sup>Institute for Particle Physics (SCIPP), University of California, Santa Cruz, California 95064, U. S. A.

### Abstract

Large area (63.6 mm x 64 mm) n-on-n silicon strip detectors have been fabricated, implementing various p-stop structures in the n-side. The detectors were characterized in laboratory and in beamtests. The beamtests showed that the individual p-stop structure collected less charge in the region between the strips than other p-stop structures.

#### I. INTRODUCTION

Large area n-on-n silicon strip detectors were fabricated out of 4-inch silicon wafers. They consisted of n-implant strips in nbulk silicon for the segmented readout and a large p-pad in the backside for the initial p-n junction. The detector was designed to function, in the heavy radiation environment such as LHC, well after the type inversion of the silicon bulk and the large increase of the depletion voltage [1].

Initially and even after the type inversion, the surface of the n-side is known to have n-type characteristics due to the accumulation layer of electrons in the interface of the surface oxide and the bulk. This accumulation layer is conductive and shorts the n-strips unless the n-strips are isolated with a p-implant structure surrounding the n-strips. A conventional way is to implant all-over the surface leaving openings for the n-strips (Full-common p-stop structure).

The p-implant has a finite resistivity and the continuous p-implant may couple neighbouring n-strips capacitively. A new type of p-stop structure was proposed by isolating the p-implant individually (Individual p-stop structure) [2]. The individual pstop structure separates the n-strips but there remains an accumulation layer outside the p-stops which is continuous over the whole surface. A modified version has been proposed, which splits each n-strip region into a cell with a narrow p-implant line and place the individual p-stop frame within the cell (Combined p-stop structure) [3]. This structure will cut the continuous accumulation layer.

The prototype detectors were fabricated with six regions of these p-stop structures. We evaluated the p-stop structures for interstrip capacitance, efficiency, charge-collection and noise performance.

#### II. N-ON-N SILICON STRIP DETECTOR

## A. Detector

The specification of the fabricated detector is summarized in Table 1. The silicon strip detector was named "nn80AC" since the detector had n-strips on n-bulk, a strip pitch of 80  $\mu$ m, and an AC coupling readout configuration. The detector had 768 readout strips divided into 6 zones with 128 strips per zone. The zones had combinations of p-stop structure and width of readout metal as listed in Table 2. Zones from 1 to 4 had the same strip and metal width but different p-stop structures. Zones from 4 to 6 had the same p-stop structure but different metal widths. The different metal width is irrelevant in this analysis.

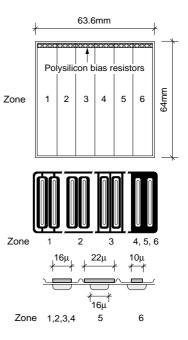

The detector, p-stop structures, and strip widths are indicated schematically in Figure 1. The p-stop structures of interest were Zones 2 (Individual), 3 (Combined), and 4 (Full-common). Zone 1 (Slit-common) was implemented to differentiate the effect of continuous and interrupted accumulation layers.

#### B. Modules

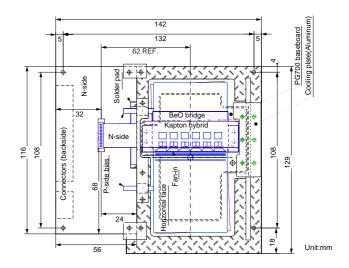

In order to measure the efficiency, charge collection, and noise, two "modules" were constructed using the detectors and a set of readout LSI's: LBIC for the preamplification, shaping, and discrimination, and CDP for buffering the on-off binary hit pattern [4]. One type of module was made by placing the readout hybrids near the middle of the detectors as shown in Figure 2, called the "Centre-tap" module. The other design was

<sup>&</sup>lt;sup>1</sup> Present address: Physics division, LBNL

made by placing the hybrids at one end of detectors, called the "End-tap" design. The data presented in this paper come from both modules.

In the modules two sets of two detectors were glued on top and bottom of a heat conducting baseboard. Two detectors on one side were daisy-chained to make a strip length of 12 cm. The heat conducting baseboard was prototyped with a pyrolytic graphite (PG700) which had a high thermal conductivity, about 300 W/m/K [5]. The top and the bottom detectors were rotated by 40 mrad relative to each other to make a stereo measurement of the positions of passing charged particles. The module was attached to an external PC board which also carried electronics to transmit and receive the signals over 20 m distance from the module to the backend electronics.

Table 1. Specification of n-on-n single-sided silicon strip detector (nn80AC)

| Detector type:             | N-bulk, n                                                                    | strip, AC-coupled, Single-sided       |  |  |  |

|----------------------------|------------------------------------------------------------------------------|---------------------------------------|--|--|--|

| Bulk:                      | N-bulk, 300 µm thick                                                         |                                       |  |  |  |

| Resistivity:               | 4~8 kΩcm                                                                     |                                       |  |  |  |

| Size (Outer):              | $6.36 \text{ cm} \times 6.4 \text{ cm} \text{ (width} \times \text{length)}$ |                                       |  |  |  |

| N-sensitive area:          | Width: $770 \times 80 \mu m = 61.6 mm$                                       |                                       |  |  |  |

|                            | Length: 62 mm                                                                |                                       |  |  |  |

| P-side structure:          | re: DC-coupled pad                                                           |                                       |  |  |  |

|                            | oreakdown ≥300V                                                              |                                       |  |  |  |

| Surface protection         | SiO <sub>2</sub> passivation                                                 |                                       |  |  |  |

| Number of N-strips:        | $(128 \times 6 \text{ zones}=768 \text{ readouts})+2 \text{ dummies}$        |                                       |  |  |  |

| N-strip isolation:         | Various p                                                                    | -stop structures (Table II)           |  |  |  |

| N-strip parameters:        |                                                                              |                                       |  |  |  |

| Polysilicon bias resistor: |                                                                              | 1.5±0.5 MΩ                            |  |  |  |

| Strip pitch:               |                                                                              | 80 µm                                 |  |  |  |

| Readout pitch:             |                                                                              | 80 µm                                 |  |  |  |

| Implant width:             |                                                                              | 16 μm                                 |  |  |  |

| Width of Al. readout:      |                                                                              | 16 µm, and others (Table II)          |  |  |  |

| P-stop width:              |                                                                              | 43 µm, and others (Table II)          |  |  |  |

| Al. thickness:             |                                                                              | 1.5 μm                                |  |  |  |

| Resistance of Al. readout: |                                                                              | ≤20 Ω/cm                              |  |  |  |

| Resistance of implant:     |                                                                              | ≤100kΩ/cm                             |  |  |  |

| AC-coupling:               |                                                                              | $SiO_2 0.25 \mu m$ + $SiN 0.05 \mu m$ |  |  |  |

|                            |                                                                              |                                       |  |  |  |

| Table 2.                    |  |  |  |  |  |

|-----------------------------|--|--|--|--|--|

| N-implant and p-stop widths |  |  |  |  |  |

|      | -                |            |                                  |        |

|------|------------------|------------|----------------------------------|--------|

| Zone | P-stop structure | Metal [µm] | P-stop [µm]                      | No.    |

|      |                  |            |                                  | strips |

| 1    | Slit-common      | 16 µ       | 2 x 18 μ                         | 128    |

| 2    | Individual       | 16 µ       | 2 x 18 μ                         | 128    |

| 3    | Combined         | 16 µ       | $2 \; x \; 11 \; \mu + 6 \; \mu$ | 128    |

| 4    | Full-common      | 16 µ       | 44 μ                             | 128    |

| 5    | Full-common      | 22 μ       | 44 μ                             | 128    |

| 6    | Full-common      | 10 µ       | 44 μ                             | 128    |

Figure 1: Schematic diagram of the detector (top), p-stop structures (middle), and strip widths (bottom). Zones are: 1=Slit-common, 2=Individual, 3=Combined, 4, 5, 6=Full-common (metal=16, 22, 10 μm, respectively)

Figure 2: "Centre-tap" module, mounted on a PC board for data communication. Strip runs vertically. The bottom detectors were rotated 40 mrad to the top detectors. A pitch-adapting "Fan-in" was used to match the strip pitch of 80  $\mu$ m and the pad pitch of 43  $\mu$ m of LBIC's.

## **III. MEASUREMENTS**

# A. Interstrip capacitance

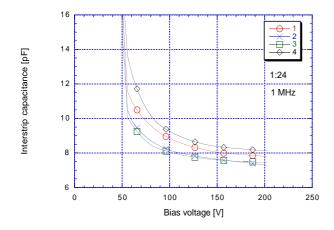

In order to characterize and compare the zones, capacitance between the strips, so-called "interstrip capacitance", was measured for one strip relative to 24 strips total in adjacent neighbours, i.e., 12 strips per side. The results for Zones, from 1 to 4, are shown in Figure 3. There were systematic errors of at most 0.5 pF in the measurement.

A strong variation of the interstrip capacitance was observed below 60 volts bias voltage. This is an indication that below depletion the n-side is shorted. Above this bias voltage, the interstrip capacitances decreased slowly. They did not show saturation even at 200 volts. There are two sources which may cause the slow decrease. One is the p-stop implant. Although it is shallow, it requires the electric field to deplete. The other is an accumulation layer in the interface of the passivation oxide and the bulk. The oxide-bulk interface contains interface states which are charged up positively and attract electrons which form a conductive accumulation layer. Apart from the global behaviour, the individual and the combined p-stop structures had the least capacitance.

Figure 3: Inter-strip capacitances in Zones 1(slit-common), 2(individual), 3(combined), and 4(full-common), measured at 1 MHz and 1 strip against neighbour 24 strips. The slow decrease of the capacitance above 60 volts is a reflection of conductive layer between the n-strips.

## B. Beamtests

Two beamtests were carried out for the fabricated modules using 4 GeV/c pions from the 12 GeV proton synchrotron at KEK. Two modules were sandwiched with high precision silicon-strip detector "telescopes". The distance between the telescopes was about 74 mm and the two modules were placed at near equal spacing. Incident particles were triggered by the co-incidence of three scintillation counters with an area of 20 mm x 20 mm.

Each telescope module was made of two single-sided strip detectors with their strips in orthogonal directions: one was in the horizontal direction, X, and the other in the vertical direction, Y. The silicon-strip detector was made of an implant strip pitch of 25  $\mu$ m and a readout pitch of 50  $\mu$ m. The sensitive region was 19.2 mm x 19.2 mm with a number of readout channels being 384. Signal pulse heights were read out and the resulting spatial resolution was about 5  $\mu$ m [6].

Data were collected at bias voltages of 80, 120, 160, and 200 volts. Threshold voltage of the discriminator was varied and expressed in charge in the unit of femto-Coulomb (fC) according

to a common calibration curve.

## C. Response in the strip and inter-strip regions

Although the electronics was calibrated in laboratory, the calibration in the beamline was not as good as we expected. Consequently, an in-situ calibration was adopted in this analysis. The gain of the different zones was obtained with the beam by assuming that the charge collection near the readout strip was the same in different zones at very high bias voltages.

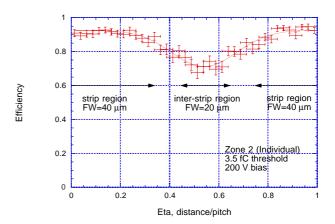

In order to define the near-strip region, the efficiency for detecting particles was mapped out between adjacent two readout strips. The detection efficiency was defined by counting hits or clusters of hits within  $\pm 250 \ \mu m$  from the interpolated position of a track given by the precision telescope hits. An example of the plot is shown in Figure 4. The horizontal axis, "Eta", was the distance from one strip to the adjacent strip normalized with the pitch of the strips which was 80  $\mu m$  in this detector.

Although less pronounced at low thresholds, the loss of efficiency in the region between the strips was evident in the high threshold. By fitting a Gaussian, the "inter-strip" region was defined with a full-width of 20  $\mu$ m around the minimum. The "strip" region was defined with a full-width of 40  $\mu$ m around the complementary point to the minimum, which left 10  $\mu$ m gap between the strip and the inter-strip regions. The definition was made for one high threshold at 200 volts and then applied to other thresholds and bias voltages uniquely.

Figure 4: Efficiency as a function of "Eta", the normalized distance between adjacent two strips. The minimum was obtained by fitting Gaussian. The inter-strip region was defined around the minimum with a full width of 20  $\mu$ m. The strip region was defined around the complementary point to the minimum with a full width of 40  $\mu$ m.

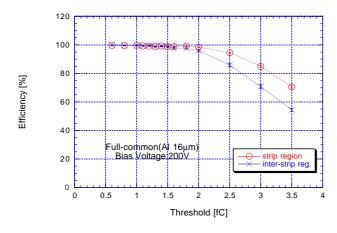

An example of efficiency variations as a function of threshold is shown in Figure 5. The efficiency curve is the integral of pulse height distribution above the threshold. The threshold of 50% efficiency is corresponding to the median pulse height of the deposit charge in one strip. In order to calibrate the gain of the electronics, the threshold of 90% efficiency was obtained by fitting an Error function, i.e., the integral of Gaussian function as an approximation of the integral of Landau distribution, to the efficiency variation. The gains of zones were normalized to the average threshold of the strip regions. Although the 90% efficiency threshold is not the median pulse height, it is a parameter correlated to the collected charge.

Figure 5: An example of the efficiency variation as a function of the threshold in strip (circle) and inter-strip (cross) regions.

# D. Comparison of losses in the inter-strip regions

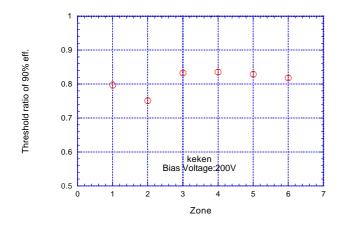

As seen in Figure 4 and Figure 5, there were losses of collected charges in the inter-strip regions. The losses were quantified with the threshold ratio of 90% efficiency of the inter-strip region over that of the strip region. The result is shown in Figure 6 for the end-tap module and at the bias voltage of 200 volts. Since we took the ratio, the gain variation was cancelled out even without the calibration of the gains in the previous section. The statistical errors were as small as the size of the circles.

Figure 6: Threshold ratios of 90% efficiency of the inter-strip region over the strip region. The ratio corresponds to the ratio of collected charge in the region. A larger loss was observed in Zone 2, the individual p-stop structure.

In general, there was about 20% less charge in the inter-strip region than in the strip region. The main source would be attributed to the sharing of charge into two strips. The charges observed in the strips are induced images of the drifting charges in the silicon. Since the efficiency in this analysis is that of a single strip, the observed charge is less when the image is doubled.

The ratios of Zone 2 (individual) and 1 (slit-common) are less than those of other zones. The ratios of Zones 3 to 6 are similar. The existence of the accumulation layer in Zone 2 and 1 would be the source of extra loss of the charge, and indicated that the continuous accumulation layer would be worse than the interrupted.

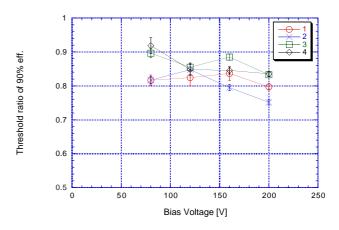

The bias voltage dependence of the ratios is shown in Figure 7 for Zones from 1 to 4. Less charges were observed in Zone 1 and 2 at all voltages, although it was less clear at 120 volts. The other trend in the bias voltage dependence was that the loss became less as the bias voltage was decreased. This may indicate that more charge would be collected in the interstrip region when the bias voltage was decreased.

Figure 7: Bias voltage dependence of the threshold ratios of 90% efficiency. The charge collection was systematically lower in Zone 1 (slitcommon) and 2 (individual p-stop).

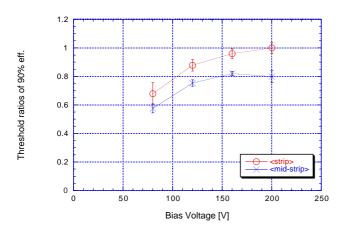

The threshold ratios averaged over zones is plotted in Figure 8. The thresholds were divided by the threshold of the strip region at 200 volts. Both in the strip- and inter-strip regions, the collected charges increased as the bias voltage was raised, although the inter-strip region charge seemed to saturate over 160 volts. The data indicated that the charges collected were less at decreased bias voltages and the difference of losses in the strip and inter-strip regions became less prominent.

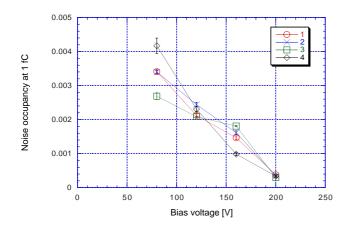

## E. Noise occupancy

Since the interstrip capacitance is a major contributor to the intrinsic noise, it is of interest how the capacitance relates with the noise in the modules. The noise was quantified as the occupancy in the strips. The occupancy was the fraction of the fired strips over the total number of strips accumulated in the triggered events. Hits associated with the triggered tracks were eliminated by eliminating the strips in the window twice-wider than that of the efficiency calculation around the triggered tracks.

The bias voltage dependence of the occupancies in Zones were plotted in Figure 9. In order to normalize the occupancies

Figure 8: Threshold ratios of 90% efficiency averaged over zones in the strip and the inter-strip regions. The thresholds were divided by the threshold of the strip region at 200 volts.

in different zones, the thresholds were re-scaled so that the thresholds of  $1 \times 10^{-3}$  occupancy at 200 volts of Zones were to be the same. This was done after the gain calibration with the strip region. The occupancies at the re-scaled threshold of 1 fC were then plotted as a function of the bias voltage.

Figure 9: Bias voltage dependence of noise occupancy at 1 fC after rescaling the gain and threshold

A gross feature of the bias voltage dependence is a near-linear dependence of the occupancy on the voltage. The occupancy increased about 8 times by decreasing the bias voltage from 200 to 80 volts. The interstrip capacitance was increased by about 1.5 pF and with a typical capacitance dependence of the intrinsic noise of electronics, the occupancy would increase about 4 times. Thus, the most of the increase of the noise occupancy was explained by the increase of the capacitance, but not all.

#### **IV. SUMMARY**

Large area (63.6 mm x 64 mm) n-on-n silicon strip detectors have been fabricated, implementing various p-stop structures in the n-side for the n-strip isolation. A comparison was made for conventional full-common, individual, combined, and slit-common p-stop structures.

The detectors were characterized in laboratory and in beamtests. The inter-strip capacitance showed that the individual and the combined p-stop structure had the least capacitance. The beamtests showed that the individual p-stop structure collected less charge in the region between the strips than other p-stop structures. The loss of charge in the individual p-stop structure has been traced to the built-in accumulation layer surrounding the individual p-stop structure and covers the detector.

The increase of occupancy was not completely explained by the increase of capacitance, and supports the need for overdepletion found in the charge collection.

## V. ACKNOWLEDGMENT

The authors wish to acknowledge J. Carter of Univ. of Cambridge, N. Jackson of Univ. of Liverpool, M. Tyndel of RAL, P. Sellin of Univ. of Sheffield, and A. Seiden of UC Santa Cruz for their strong support to the program.

This work was supported by Japan Ministry of Education, Science, and Culture, and Japan Society for Promotion of Science, US Department of Energy, Australian Department of Industry, Science and Tourism, and Austrian Research Council, and UK Particle Physics and Astronomy Research Council.

## VI. REFERENCES

- D. Pitzl et al., "Type inversion in silicon detectors", Nucl. Instr. Meth. A311, pp98-104, 1992

- [2] P.I. Hopman, J.P. Alexander, A.D. Foland, P.C. Kim, C.W. Ward, "Optimization of silicon microstrip detector design for CLEO III", Nucl. Instr. Metho. A383, pp. 98-108, Dec. 1996

- [3] T. Ohsugi, et al., IEEE 1997 Nucl. Scie. Symp, Albuquerque, NM

- [4] LBIC: E. Spencer et al., "A Fast Shaping Low Power Amplifier-Comparator Integrated Circuit for Silicon Strip Detectors", IEEE Trans. Nucl. Scie, Vol. 42, pp. 796-802, Aug. 1995; CDP: J. DeWitt, "A Pipeline and Bus Interface Chip for Silicon Strip Detector Read-out", Proc.IEEE Nucl. Scie. Symp., San Francisco, CA., Nov. 1993

- [5] Pyrolytic graphite data sheet, Advanced Ceramics Corporation, P.O.Box 94924, Cleveland, Ohio 44101, U.S.A; In Japan: Tomoe Engineering Co. Ltd., Daini Maruzen Building, 9-2 Nihonbashi 3-Chome, Chuo-Ku, Tokyo 103, Japan

- [6] O. Toker, S. Masciocchi, E. Nygard, A. Rudge, P. Weilhammer, "Viking: A CMOS low noise monolithic 128-channel frontend for Si strip detector readout", Nucl.Instr.Meth. A340, pp. 572-579, 1994